# AI-Optimized Semiconductor Architectures: The Convergence of Deep Learning and Custom Hardware Design

# Karthik Wali

ASIC Design Engineer ikarthikw@gmail.com

# Abstract

The integration of AI with the semiconductor design has transformed computing paradigms in a way that benefits from specifically optimised design for deep learning. This paper aims at discussing Artificial Intelligence optimized semiconductor structures where authors apply deep learning approaches to optimize hardware systems. Thus, through the employment of present-day NAS techniques and reinforcement learning, the synthesis of semiconductor circuit diagrams and their layout, power-consumption, and computing capabilities can be automatically and optimally designed. We consider different HW accelerators for AI applications: Google's TPUs, neural networks based on GPUs from NVIDIA, and application-specific programmable devices known as FPGAs. Finally, it is crucial to discuss further the role of AI in the design of semiconductors, growth strategies and trends, methods, and challenges and prospective improvements based on case studies, comparisons and benchmarks. The findings showed that various optimisations using AI lead to increased performance-per-watt efficiency, speed of computation, and the ability to support AI workloads. Last of all, we explore how AI maintains its imprint on semiconductor architectures and other factors concerning the future of the computing platform.

Keywords: Deep learning, Neural architecture search, Custom hardware design, AI accelerators, Semiconductor.

# 1. Introduction

# 1.1 The Evolution of Semiconductor Architectures

The semiconductor architectures have changed in the decades depending on the changing material, design and computation considerations. The advancements of these architectures have bore such benefits like efficiency, sharp reduction in the size and general boost in performance that have facilitated the development of the modern computing technologies. [1-4] The evolution of CRB is presented below in the following stage:

### Figure 1: The Evolution of Semiconductor Architectures

- Early Vacuum Tube Computers: The use of vacuum tubes was the older method of computing before the advent of the use of semiconductor in designing computers. For example, ENIAC the first general-purpose electronic computer is large and power consuming and tripping frequently because of failure of the vacuum tubes. Solid-state technology signified the phase in the semiconductor evolution whereas people started using solid-state device.

- The Invention of the Transistor: Transistor, invented in Bell Labs in 1947 became a major advancement to semiconductor and electronic technology since it was a substitute to the heavey vacuum tubes. Transistors gave a way to devise early integrated circuits, less power consumption, and better reliability.

- The Rise of Integrated Circuits (ICs): In 1960s two key developments came up where many numbers of transistors were realized on the similar chip known as integrated circuit. This led to the production of portable and cheap computing devices on which the first microprocessors were developed. ICs are at the heart of today's semiconductor manufacturing process known and established by ICs.

- The Birth of Microprocessors: The first microprocessor which was available in the market was Intel 4004 in the year 1971 with processing logic implemented on the chip. This shifted focus towards the personal computing with more powerful and affordable computers. The evolution that came after it nurtured further development in terms of processing power to go through an order of magnitude jump.

- The Era of Moore's Law and Scaling: Moore in his speech in the year 1965 set down what is known today as the Moore's Law and this forecasted that the number of transistors in every chip would double in two years. This trend defined the progress of the semiconductor making circuits miniaturized, relatively higher in performance with less costs involved. However, at some point transistor sizes could not be scaled down, due to engineering limitation which stemmed from physical barriers.

- **Multi-Core and Parallel Processing Architectures:** Due to the fact that clock speed scaling was no longer a viable option in the early part of this decade, complexity of the core became the center of innovation. Instead of an increase of the clock rate, the number of cores for parallel processing and

better multithreading was integrated into a single chip. It also solved problems associated with heat dissipation as the size reduced and yet computing capability increased.

- AI-Optimized and Specialized Architectures: When AI and machine learning came to the forefront; new architectures called GPUs, TPUs as well as neuromorphic chips were integrated into semiconductors. These are designed to support parallelism which makes artificial intelligence inference and training faster. Advanced and optimized semiconductor platforms for artificial intelligent applications are apparently fuelling this area of advancement.

- The Future of Semiconductor Architectures: Quantum and Beyond: The current trends that are being observed to define the future of the evolution of semiconductors include quantum computing, three dimensional stacking, and chiplets. Quantum processors make use of quantum bits or qubits to solve vast and complex calculations that are far much faster than what classical processors can do. On the other hand, chiplet based architectures offer more modularity, scalability as well as connectivity and power efficiency. These concepts are geared at extending the clock's ability beyond the existing boundaries of semiconductor scaling and open up a new frontier of computing.

### 1.2. Role of AI in Semiconductor Optimization

AI has made an evolutionary breakthrough in the field of Semiconductor Design as it is now a tool for automation, improvement of efficiency, and decreasing of the design complexity. Previously, chip layout design process required a great deal of human intervention and followed the rules of thumb and guidelines which considerably took a lot of time and was subjective and imprecise. Substantial developments in recent years of Artificial Intelligence especially Deep Learning and Reinforcement learning have turned out to be very helpful for managing some of the essential steps such as transistor placement, power optimization, and performance tuning. The major use of AI in semiconductors is found in the floor planning process in which the various designs are optimized based on models which analyse several layouts. In a similar way, Google's deep reinforcement learning has shown in developing chip layouts that it only takes a fraction of the time needed to be utilized by engineers. This enhances the rate of design or the development cycle and the utilization of chip area, thus contributing to the improvement of power utilization and the overall cost of production. [5,6] One of the key and significant areas that involve the use of AI is power and thermal management. The use of AI makes it easier for the system to forecast power usage and how the power must be shared so that there is less wastage of electricity. Machine learning will also help in finding out areas of high thermal densities within a given chip and then help in readjusting the position of components in a way that would help with heat dissipation and at the same time extending the lifespan of the chip. The use of artificial intelligence in design verification and testing of the semiconductor adds to the reliability of the product. Existing approaches often call for various extensive simulations, while using artificial intelligence makes it easier to find possible design flaws and prevent long debugging processes as a result, the yield rates will be higher. Also, AI is able to create a variety of logic gates and their interconnections for the circuit automatically and make computations faster than in circuits with a higher number of chips. While designing semiconductors are getting more complex, AI is proving to be an enabler in terms of fast and efficient design used in optimizing cost and performance. As latest developments in machine learning and other AI based platforms for EDA continue to develop further, it is envisaged that semiconductors will be enhanced through self-learning with little interference from humans to optimize for efficiency.

#### **1.3.** The Need for Custom AI Hardware

With the increasing sophistication of the AI, there is a greater need for speed and efficient power consumption that have propelled uniqueness in AI hardware. Prior processors are overburdened by such demands, let alone CPUs and even GPUs in training, real-time inferences, and huge data processes in deep

learning models. This has led to the need for dedicated AI accelerators that are designed to enhance efficiency, cut back on latency, and is energy saving. Among the main goals of creating specific AI chips, power consumption is of chief concern. AI operations include matrix manipulations and tensor computations which are complex in regards to computation. GP processors are not efficient in those operations and as such they lead to wastage of power. Specialized AI chips including Google's Tensor Processing Units or TPUs provide efficient power usage in tensor computations as compared to GPUs and CPUs. Also, similar to the human brain, neuromorphic chips provide extremely low power consumption of AI for edge computations. Other important factors that make use of custom AI chip include; Also important to consider when it comes to custom AI chip is; The conventional system hardware makes some limitations for deep learning tasks in order to produce a real-time AI for larger applications like self-driving car, robots, real-time speech recognition, etc. Custom AI consists of optimized arch; it means that more than one operation happens in parallel in custom AI which makes computation time less and better. Both FPGAs and ASICs are often employed to implement domain-specific AI hardware with more programmability to optimize resource consumption. With constant development in technologies and maturity of artificial intelligence as a field, dedicated systems will be needed more and more. Particularly, custom AI chips will become essential for new generations of AI devices as well as for cloud services based on machine learning. Advancements in the sector of hardware imply a more effective operation, higher efficiency, and lower prices of the developed AI systems that help to expand the limits of AI's advancement.

### 2. Literature Survey

# 2.1. Early Approaches in Semiconductor Design

Before the conceptualization of AI, semiconductor design was only based on rules and heuristics as well as EDA tools. These conventional techniques incorporated a lot of human knowledge which meant engineers directly set design guidelines and optimized the chip geometry through iteration. The process was time consuming and every single step needed a good level of domain expertise to get the expected level of output. [7-10] EDA tools were useful up to a certain extent in helping people perform some routine jobs like circuit simulation and layout verification; it had certain static predetermined operations and algorithms and they could not on their own upgrade in response to new upcoming designs. The complexity of the chip architectures demand higher efficiency, low power consumption, and fast computation speed In the previous years, they could not cope up with the demands of the growing market.

#### 2.2. AI-Driven Hardware Design

As machine learning and reinforcement learning improved over the years, even in the areas of HVAC, the semiconductor industry has gradually adopted AI solutions to the hardware design. There are other approaches, including deep reinforcement learning and neural networks, in which AI models have become useful tools in the optimization of chip layouts in the specific area, power distribution as well as the performance characteristics. One example of this is when Google applied deep reinforcement learning for the chip floor planning, wherein the AI is trained to self-improve on arranging components on a silicon die. When compared with traditional method that formulates design based on previously defined rule of thumb, AI-based design has the capability to self adapt to new constraints and objectives and cost much less time on generating design. It also helps in predictive analysis via simulation which helps the engineers to predict design defects regarding power efficiency, thermal management and signal integrity etc with less interference to the system.

### 2.3. Comparative Analysis of AI-Optimized and Traditional Semiconductor Design

This change from the previous generation semiconductor designing to the current artificial intelligence approach has brought about changes in most of the chip designing aspects. Traditional design utilizes rulebased method, where engineers enhance the chip layouts through applying certain measures which make the flow slow and costly. However, AI-optimized design does this using machine learning algorithms that increase learning from the work challenges improving efficiency and automating the process. Another benefit of the use of AI in the design process is power functionality; in the traditional approach, design is performed iteratively and accomplishes moderate level of efficiency, while the AI model can scan multiple design abstracts and identify the best configurations that will enhance the level of energy consumption. Further, design with the help of AI also helps to improve the speed of computation by planning and optimizing on different procedures of the design in an automated manner cutting the time for floor planning and optimization. This can be done through AI-based methods that eliminate the need for human input in the decision making process to a large extent, as compared to conventional processes.

# 3. Methodology

# **3.1. AI-Based Optimization Techniques in Semiconductor Design**

- Neural Architecture Search (NAS): NAS is a type of the ML technique that involves the optimization of the chip architectures from a given network and without the human intervention. In the field of semiconductors, NAS is used to search for the best solutions in chip layouts, circuit structures, and processing units designing much more possibilities than it is possible to manually check by the engineers. [11-15] SOTA design follows certain rules of thumb, whereas, NAS undergoes certain exploration using AI and evolutionary algorithms to find out the best set of architectural structures or similar which yields the best performance along with least power consumption at least chip area. Through sequential re-evaluation of different strategies for the architecture of the neural network, NAS can develop efficient designs optimal for the underlying computational requirements for various fields such as, edge computing AI accelerator, and high-performance computing chips. It is useful in the current world of semiconductor improvement as it reduces the design time and therefore the time taken to produce the design making it efficient.

- Reinforcement Learning (RL): Eight papers presented at the conference thoroughly discussed various aspects of RL's applications in semiconductor design lawsuit, including power and thermal management and chip placement and interconnects. This process was executed by putting the environment in an agent with an aim of helping the agent get rewards based on what he or she does, enhancing the agent's choices as they spend as much time as possible, in the best state. In the semiconductor optimisation, the application of RL helps in its decision making process such as placement of components, routing of interconnections, and power supply. For example, reinforcement learning has been utilised efficiently by Google for chip floor planning and the outcomes of the same have been found to surpass the manually designed layouts in terms of speed, power, and performance. Additionally, RL-based methods are very useful for dynamic power and thermal management techniques, where AI models learn the voltage control, workloads distribution and heat control in real time. As a result of dispensing with rule-based algorithms to be substituted by such innovative AI decision-making capabilities by RL, advances the semiconductor design automation in the areas of speed, power consumption, as well as cost of producing chips.

# **3.2. AI-Optimized Hardware Architectures**

• **Tensor Processing Units (TPUs):**TPUs stand for Tensor Processing Units and are developing by Google as an application-specific processor to maximize the performance of deep neural networks

computations mostly during the training and inference processes. TPUs are dissimilar from regular CPUs and GPUs since they are only designed for tensor processing, thus having matrix dot products and systolic arrays incorporated within them. This architecture thus enhances the computation of deep learning in a way that enhances throughput with a fast rate in addition to using less power. As of now TPUs are widely integrated into cloud based computer applications which include natural language processing, image recognition and large scale machine learning models. As a result, GPUs are best suited for huge parallel processing tasks such as deep reinforcement learning and neural architecture search to drive semiconductor design using artificial intelligence.

• Neuromorphic Chips: Neuromorphic chips are relatively new kinds of computing devices that are developed to be optimized for AI, these chips are designed to mimic the human brain in many ways including structural organization and resulting functionality. They are built based on the spiking neural networks (SNNs) instead of the typical artificial neural networks; therefore, the computation is event-driven which means that the computation takes place only when necessary and not at the right time ticks. This leads to the reduction in power consumption which makes neuromorphic chips suitable for real time computation use in artificial intelligence such as in robotics, edge computing and autonomous systems. Today, just few companies like Intel with Loihi chip and IBM with True North chip have worked on developing neuromorphic chips which show the adaptability of the chip in learning and cognitive processing. In this view the memory and compute are integrated in the manner closely resembling the brain, thus removing data movement bottlenecks and boosting the efficiency of AI operations.

**Figure 2: AI-Optimized Hardware Architectures**

• FPGAs and ASICs: FPGAs and ASICs are two critical forms of hardware implementation of AI adaptable to the requirements of specific applications. FPGAs are types of logic circuits that may be configured and reconfigured after their production to respond to market needs, thus being very versatile in the dynamic AI jobs. They are easily reprogrammable, have parallel processing ability and hence preferred for tasks such as prototyping as well as real-time inferencing. ASICs are entirely different and are specially made for a specific AI application that serves as a better solution in terms of integrated performance, power usage, and cost when the technology is going to be deployed in bulk. They are used in other AI accelerators, for instance, Google TPUs and Tesla AI chips for self-driving cars. However, ASICs provide much higher efficiency in comparison to other solutions, but their inherent inability to adapt to any changes does not allow using them in any practical application of AI, which has a clearly defined high demand for repeatability. In sum, FPGAs and ASICs are both

important solutions to address AI computations in different sectors, ranging from cloud to embedded AI systems.

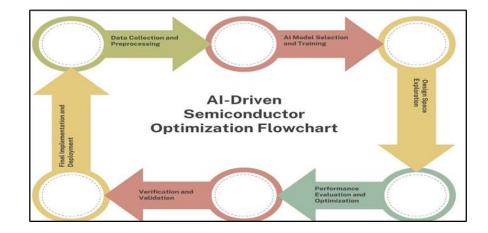

# 3.3. AI-Driven Semiconductor Optimization Flowchart

Figure 3: AI-Driven Semiconductor Optimization Flowchart

- **Data Collection and Preprocessing:** First, a large number of sets of previous chip designs, simulation data, and performance data are collected for optimization. This data is then preprocessed to remove any unintended items or variations in order to improve the reliability of the model chosen.

- AI Model Selection and Training: As for the suitable optimization goals, these may include the choice of machine learning algorithms such as neural networks or reinforcement learning models. It then uses the data involving the past design of semiconductors to build and enhance the ability to make decisions in Semiconductor optimization.

- **Design Space Exploration:** AI comprehensively tests various chip layout and architecture topologies as well as power distribution schemes and performance-vs power consumption options are tested. This step assists in selection of the most efficient design given that there will not be much intervention from the operator.

- **Performance Evaluation and Optimization:** The AI model measures each of the generated designs by means of such quantifiable features as power consumption, speed, and thermal characteristics. Optimisation processes improve the design step-by-step so that there is the optimal performance/cost point.

- Verification and Validation: The selected or the most optimal design is then taken through a series of tests and validations that comprise of testing through simulation and actually physical tests to prove the reliability of a design in the specific industry which it is to be designed for and to meet the functional requirements required of it.

- **Final Implementation and Deployment:** The semiconductor design process is then complete after validation to be fabricated in the next process. The use of artificial intelligence also avails the factors of easing the design process, the time taken to complete the design and the performance as compared to the conventional methods.

# 4. Results and Discussion

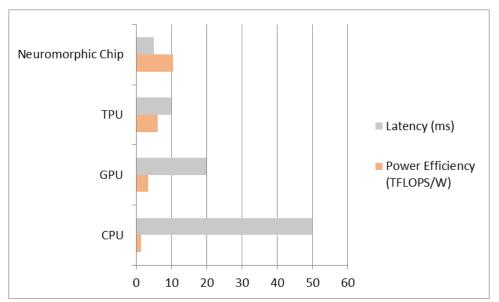

# 4.1. Benchmarking AI-Optimized Hardware

Since AI has been analyzed to require hardware-sufficient resources to create optimized solutions, a comparison is done with traditional architectures. The performance comparison of the hardware platforms

based on power efficiency and latency are given in the table 1. Specialized hardware like Tensor Processing Unit (TPU), Neuromorphic Chips offers high power efficiency and lesser latency as compared to Classical CPU and GPU.

| Table 1. 1 erformance wetries of Al-Optimized vs. Conventional fratuware |            |            |              |

|--------------------------------------------------------------------------|------------|------------|--------------|

| Hardware                                                                 | Power      | Efficiency | Latency (ms) |

|                                                                          | (TFLOPS/W) |            |              |

| CPU                                                                      | 1.5        |            | 50           |

| GPU                                                                      | 3.5        |            | 20           |

| TPU                                                                      | 6.2        |            | 10           |

| Neuromorphic Chip                                                        | 10.5       |            | 5            |

Table 1: Performance Metrics of AI-Optimized vs. Conventional Hardware

- CPU (Central Processing Unit): CPU stands for Central Processing Unit and it is the main computer processor used for carrying out different general computations. However, they are low in power conversion efficiency to provide only 1.5 TFLOPS/W and possess high latency of 50 ms because of the sequential nature of the computing methodology. CPUs can be considered unsuitable for parallel computations but they are still irrational for AI tasks, while control logic and other computations belongs to their domain.

- **GPU (Graphics Processing Unit):** GPUs are inherently designed to be parallel processors and therefore will perform way better than CPUs in AI and deep learning applications. Based on the peak efficiency of 3.5 TFLOPS/W and cutting the latency of 20 ms, GPU is more superior than CPU in HPC and deep learning. Due to its thousands of cores, it can support multiple operations at once making them suitable for training and application of AI models but they still are energy hogs.

- **TPU (Tensor Processing Unit):** TPUs are, in fact, Google's proprietary accelerated computing processors specifically designed for Tensor operations used in migrating deep learning technologies. In terms of power efficiency they get to 6.2 TFLOPS/W as for latency its only ten milliseconds which is far much lesser than CPUs and GPUs. One is that TPUs are particularly tuned for AI workloads particularly for training and inference of neural networks balanced with high-performance and low power consumption. They can perform matrix multiplications at a very high rate, which makes them suitable for AI associated with cloud computing.

Figure 4: Graph representing Performance Metrics of AI-Optimized vs. Conventional Hardware

• Neuromorphic Chip: Neuromorphic chips resemble the structure and function of the human brain employing spiking neural networks event-based processor. This design offers the highest power efficiency of 10.5 TFLOPS/W and ultra-low latency of 5 ms. Unlike conventional processors which always take power even when not performing a computation task, neuromorphic chips take up power only at the time of computation and hence are suitable for AI at the edge, robotics and real-time learning. They are reprogrammable and mimic the functionality of the human brain and also have a dissipation of power provision that is ultra-low which is critical for advancing AI hardware.

### 4.2. Case Study: Google's AI Floor planning

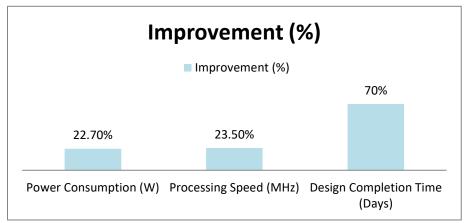

#### Table 2: Performance Gains in Google's AI-Based Floorplanning vs. Traditional Methods

| Metric                               | Improvement (%) |

|--------------------------------------|-----------------|

| Power Consumption (W)                | 22.7%           |

| Processing Speed (MHz)               | 23.5%           |

| <b>Design Completion Time (Days)</b> | 70%             |

Figure 4: Graph representing Performance Gains in Google's AI-Based Floorplanning vs. Traditional Methods

- Power Consumption Reduction (22.7%): It also announces that Google recently employed chip floor planning using the help of artificial intelligence which makes the possibility of organizing up to 45 percent smaller at scale than by using conventional approaches, and results in power saving of as much as 22.7 percent. The reinforcement learning helps in the placement of the components in such a way that the length of wires from place to place and thermal distribution reduces the energy consumption. It also increases battery lifespan for portable devices as well as decreases operational expenses for data center, and therefore, AI optimized chips are more sustainable and energy efficient.

- **Processing Speed Improvement (23.5%):** The application of AI in chip designing also enabled Google to design more advanced chips which offered a 23.5% faster in speed. The circuits are adjusted in such a way that they impend minimum signals and maximize business throughput. Therefore, more sophisticated chips can perform more AI calculations in the same second, thus enhancing the speed of real-time inference in various uses such as autonomous vehicles and cloud services.

- **Design Completion Time Reduction (70%):** Conventional chip floor planning can take several weeks or months, and usually this process involves a lot of modifications. Utilizing reinforcement learning, Google cuts down the design completion duration to 30% and thus shortens the time to

10

bring new semiconductor products to the market. In addition to enhancing cycles to realize the design, technology contribution in automating the design process averts engineers from spending their time on layout modifications and enables them to concentrate on improvements.

#### 4.3. Challenges and Future Directions

- Scalability Issues: Designing semiconductors using AI demands tremendous computational capabilities and memory capacity to solve, which brings in issues concerning scalability. Training the AI models with optimization in place requires a lot of utilization of design data which is equally time-consuming, computationally intensive and energy dependent. However, the extent of the difficulty of employing the AI-based methodologies to larger complex chips is easy to understand; complex chip designs come with complex design features and restrictions such that AI has to deal with. These causes suggest that improvement of scalability in recommender systems will depend on additional developments in the efficiency of AI models and hardware supports.

- Security Concerns: The introduction of the AI system in the design of the semiconductor brings new risks of cybersecurity threats. Adversarial attacks are specifically a very big threat for AI-optimized chips since it involves the manipulation of AI models that lead to wrong or less efficient designs. In addition, the growing use of AI tools makes it risky to apply them in the development of semiconductors, as the actual and potential design methodologies and architectures may be compromised or stolen. The major risks facing Deep Web will include and the following measures can be applied to curb it: Emphasis on stronger security frameworks Organization of better protective measures and Best policies Driven by AI.

- Ethical Considerations: First, it is important to focus on the ethical implications that are mainly seen in the area of job replacement through AI automation in the design of semiconductors. This means that semiconductor engineers and designers who used to be involved in also manual design processes that have now been resolved through AI risk of being laid off or having reduced tasks. However, the increase in uses of AI in choosing what is needed for the functions of society's important aspects as in health and defense-related chips raises questions on the ethics to be exercised to avoid circumstantial mishaps or biased effects. It is therefore necessary that the process of automation to be balanced between machines and human experts to achieve a safe integration of AI in the semiconductor industry.

#### 5. Conclusion

Artificial intelligence refer to a broad concept of mimicking the functionalities of the human mind for purposes of solving complex problems, especially in the field of designing semiconductors. Applications of AI techniques like NAS, RL, as well as deep learning increases the speed and efficiency of design and development of high performing and power efficient processors. Conventional ways of designing semiconductors were mostly human centric and based on set of conventional rules and constraints. It has, however, automates many of these tasks implying faster development cycles, lesser power consumption and better computational capabilities. An extraordinary progress in the field of AI application in semiconductors is AI-specific hardware accelerators. TPUs have been show to be very efficient in deep learning applications as a result they offered great improvements in terms of power consumption and computational speed than the conventional CPUs and GPUs. Hence, the neuromorphic chips that imitate the function of the neural circuitry within the brain are revolutionizing AI computation through enabling ultra-low power and real time computation in the edge devices. FPGAs and ASICs are also being used to an ever-increasing extent for AI workloads in specific fields to achieve better efficiency and performance. Such enhancements have

made AI-driven semiconductor architectures crucial in various uses like cloud computing and even autonomous systems or Intelligent IoT devices.

However, there are certain difficulties still present in the implementation of AI in the field of semiconductor optimization. Another key factor is computational scalability, since the training of sophisticated AI models for designing chip is a computationally and energy-intensive process. It must also be noted that this complexity of the modern semiconductor architecture is also a factor affecting scaling of AI methodologies for next-generation chips. Moreover, security becomes a major issue of conversation where AI-optimized chips possess various threats, which include adversarial attacks and risks regarding intellectual property. To address the mentioned issues, it implies innovations in the efficiency of the AI model, better security approaches, and the fabrication of semiconductors. In the future there's still much potential especially in the way how the AI-optimized semiconductor architectures will evolve. Over the time, these AI algorithms are bound to improve in their contribution to automation, efficiency and complexities in the design of chips. In future work, efforts should be devoted on enhancing the EDA tools driven by AI, enhancing power consumption level of AI models, and advancing new hardware design that supports AI integration. It is therefore the symbiotic relations that are going to be required between the artificial intelligence researchers and valuable semiconductor engineers to further advance the next generation AI perceptions to their optimal best. Thus, eliminating the current challenges and utilizing the potentials of AI, the semiconductor industry is on the verge of future improvement in terms of performance, energy efficiency, and innovation.

### References

- 1. Markov, I. L. (2014). Limits on fundamental limits to computation. Nature, 512(7513), 147-154.

- 2. Wong, D. F., & Liu, C. L. (1986, June). A new algorithm for floorplan design. In 23rd ACM/IEEE Design Automation Conference (pp. 101-107). IEEE.

- 3. Radamson, H., Simeon, E., Luo, J., & Wang, G. (2018). Scaling and evolution of device architecture. CMOS Past, Present and Future; Elsevier: Amsterdam, The Netherlands, 19-40.

- 4. Stojčev, M. K., Tokić, T. I., & Milentijević, I. Z. (2004). The limits of semiconductor technology and oncoming challenges in computer micro architectures and architectures. Facta universitatis-series: Electronics and Energetics, 17(3), 285-312.

- 5. Topol, A. W., La Tulipe, D. C., Shi, L., Frank, D. J., Bernstein, K., Steen, S. E., ... & Ieong, M. (2006). Three-dimensional integrated circuits. IBM Journal of Research and Development, 50(4.5), 491-506.

- Shukla, S. K., Murthy, C. N. S., & Chande, P. K. (2015). A survey of approaches used in parallel architectures and multi-core processors, for performance improvement. In Progress in Systems Engineering: Proceedings of the Twenty-Third International Conference on Systems Engineering (pp. 537-545). Springer International Publishing.

- Welser, J., Pitera, J. W., & Goldberg, C. (2018, December). Future computing hardware for AI. In 2018 IEEE International Electron Devices Meeting (IEDM) (pp. 1-3). IEEE.

- 8. Dossis, M. (2014). Synthesis of Custom Hardware from ADA with Artificial Intelligence Techniques. Adv Robot Autom, 3(121), 2.

- 9. White, K. P., Trybula, W. J., & Athay, R. N. (1997). Design for semiconductor manufacturing. Perspective. IEEE Transactions on Components, Packaging, and Manufacturing Technology: Part C, 20(1), 58-72.

- 10. Oba, F., & Kumagai, Y. (2018). Design and exploration of semiconductors from first principles: A review of recent advances. Applied Physics Express, 11(6), 060101.

- Ghahramani, M., Qiao, Y., Zhou, M. C., O'Hagan, A., & Sweeney, J. (2020). AI-based modeling and data-driven evaluation for smart manufacturing processes. IEEE/CAA Journal of Automatica Sinica, 7(4), 1026-1037.

- 12. Li, Y. (2017). Deep reinforcement learning: An overview. arXiv preprint arXiv:1701.07274.

- 13. Arulkumaran, K., Deisenroth, M. P., Brundage, M., & Bharath, A. A. (2017). Deep reinforcement learning: A brief survey. IEEE Signal Processing Magazine, 34(6), 26-38.

- 14. García, S., Ramírez-Gallego, S., Luengo, J., Benítez, J. M., & Herrera, F. (2016). Big data preprocessing: methods and prospects. Big data analytics, 1, 1-22.

- 15. Morris, P. R. (1990). A history of the world semiconductor industry (No. 12). IET.

- Holbrook, D., Cohen, W. M., Hounshell, D. A., & Klepper, S. (2000). The nature, sources, and consequences of firm differences in the early history of the semiconductor industry. Strategic Management Journal, 21(10-11), 1017-1041.

- 17. Leppelt, P., Hassine, A., & Barke, E. (2006, December). An approach to make semiconductor design projects comparable. In 7th Asia Pacific Industrial Engineering and Management Systems Conference (APIEMS 2006) (pp. CD-ROM).

- Kumar, N., Kennedy, K., Gildersleeve, K., Abelson, R., Mastrangelo, C. M., & Montgomery, D. C. (2006). A review of yield modelling techniques for semiconductor manufacturing. International Journal of Production Research, 44(23), 5019-5036.

- 19. Holbrook, D. (1995). Government support of the semiconductor industry: Diverse approaches and information flows. Business and Economic History, 133-165.

- 20. Beu, L., & Mendicino, L. (1997). Application of design for environment concepts to the semiconductor industry. Environmental progress, 16(4), 245-250.